|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              | REVIS                                            | SIONS                                        |                             |                             |                                      |                              |                                         |                        |        |  |

|----------|---------------------|--------|--------------------------|---------------|---------------|-----------------------|---------------------------|------------------------------------------------------------------|----|---|------------------------------|--------------------------------------------------|----------------------------------------------|-----------------------------|-----------------------------|--------------------------------------|------------------------------|-----------------------------------------|------------------------|--------|--|

|          |                     |        |                          |               | LTR DESCRIPTI |                       |                           |                                                                  | ON |   |                              |                                                  | D                                            | DATE APPRO                  |                             |                                      | OVED                         |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

| Prepared | l in acc            | cordan | ce with                  | n ASME Y      | (14.24        |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      | Ve                           | endor i                                 | tem di                 | rawing |  |

| REV      |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

| PAGE     | 1                   |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

| REV      |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

| PAGE     |                     |        |                          |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

| REV STA  |                     |        | REV                      |               |               |                       |                           |                                                                  |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

| OF PAG   | ES                  |        | PAG                      | E             | 1             | 2                     | 3                         | 4                                                                | 5  | 6 | 7                            | 8                                                | 9                                            | 10                          | 11                          | 12                                   |                              |                                         |                        |        |  |

| PMIC N/  | <b>A</b>            |        |                          | PREPA         |               |                       | Nauv                      | on                                                               |    |   | DLA LAND AND MARITIME        |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        |                          | Phu H. Nguyen |               |                       |                           | COLUMBUS, OHIO 43218-3990<br>http://www.landandmaritime.dla.mil/ |    |   |                              |                                                  |                                              |                             |                             |                                      |                              |                                         |                        |        |  |

|          |                     |        | Original date of drawing |               |               |                       |                           |                                                                  |    |   |                              |                                                  | http                                         | ://ww                       | w.lan                       | dandn                                | naritir                      | ne.dla                                  | <u></u>                |        |  |

|          | YY MM DD            |        | ng                       | CHECK         |               |                       | Name                      | 00                                                               |    |   | тіт                          | LE                                               | <u>http</u>                                  | ://ww                       | w.lan                       | dandn                                | naritir                      | ne.dla                                  | <u>mil</u> /           |        |  |

| 12-11-15 |                     |        | ng                       |               |               | Phu H.                | Nguy                      | en                                                               |    |   | МІС                          | ROC                                              | <u>http</u><br>CIRCI                         | JIT,                        | w.lan                       | andn<br>AR,                          | DUA                          | ne.dla                                  | <u>i.mil</u> /<br>JRRE | ENT    |  |

|          |                     |        | ng                       | CHECK         | VED B         | Phu H.<br><b>Y</b>    |                           |                                                                  |    |   | MIC<br>OU                    | ROC                                              | <u>http</u>                                  | JIT,                        | <u>w.lan</u><br>LINE<br>LEL | andn<br>AR,<br>INPU                  | DUA                          | ne.dla<br>L CL<br>6-BIT                 | <u>mil</u> /<br>JRRE   | INT    |  |

|          | 12-11- <sup>-</sup> |        | ng<br>-                  |               | VED B         | Phu H.                |                           |                                                                  |    |   | MIC<br>OU <sup>-</sup><br>MU | ROC<br>TPU<br>LTIP                               | <u>http</u><br>CIRCI                         | JIT,<br>ARAL<br>G DA        | LINE<br>LEL<br>CW           | AR,<br>INPU                          | DUA<br>T, 16                 | ne.dla<br>L CL<br>6-BIT<br>ADR/         | <u>mil</u> /<br>JRRE   | INT    |  |

|          | 12-11- <sup>-</sup> |        | ng<br>-                  |               | VED B         | Phu H.<br><b>Y</b>    | s M. H                    | ess                                                              |    |   | MIC<br>OU<br>MU<br>RES       | ROC<br>TPU<br>LTIP                               | <u>http</u><br>CIRCI<br>F, PA<br>LYIN<br>OR, | JIT,<br>ARAL<br>G DA<br>MON | LINE<br>LEL<br>CW           | andn<br>AR,<br>INPU<br>ITH 4<br>THIC | DUA<br>T, 16<br>-QU<br>SILIC | ne.dla<br>AL CU<br>6-BIT<br>ADR/<br>CON | <u>mil</u> /<br>JRRE   | NT     |  |

|          | 12-11-              |        | ng<br>-                  | APPRO         | VED B         | Phu H.<br>Y<br>Thomas | s M. Ho<br>E <b>NT. N</b> | ess                                                              |    |   | MIC<br>OU<br>MU<br>RES       | ROC<br>TPU<br>LTIP<br>SIST                       | <u>http</u><br>CIRCI<br>F, PA<br>LYIN<br>OR, | JIT,<br>ARAL<br>G DA<br>MON | LINE<br>LEL<br>CW           | AR,<br>INPU                          | DUA<br>T, 16<br>-QU<br>SILIC | ne.dla<br>AL CU<br>6-BIT<br>ADR/<br>CON | <u>mil</u> /<br>JRRE   | NT     |  |

|          | 12-11- <sup>-</sup> |        | ng<br>-<br>-             | APPRO         | VED B         | Phu H.<br>Y<br>Thomas | s M. Ho<br>E <b>NT. N</b> | ess<br>IO.                                                       |    |   | MIC<br>OU<br>MU<br>RES       | ROC<br>TPU <sup>-</sup><br>LTIP<br>SIST<br>3 NO. | <u>http</u><br>CIRCI<br>F, PA<br>LYIN<br>OR, | JIT,<br>ARAL<br>G DA<br>MON | LINE<br>LEL<br>CW           | andn<br>AR,<br>INPU<br>ITH 4<br>THIC | DUA<br>T, 16<br>-QU<br>SILIC | ne.dla<br>AL CU<br>6-BIT<br>ADR/<br>CON | <u>mil</u> /<br>JRRE   | INT    |  |

## 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance dual current output, parallel input, 16-bit multiplying DAC with 4-quadrant resistor microcircuit, with an operating temperature range of -55°C to +125°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/12651<br>Drawing<br>number | - <u>01</u><br>Device type<br>(See 1.2.1) | XBIICase outlineLead finish(See 1.2.2)(See 1.2.3)                |                     |

|--------------------------------|-------------------------------------------|------------------------------------------------------------------|---------------------|

| 1.2.1 Device type(s).          |                                           |                                                                  |                     |

| Device type                    | Generic                                   | Circuit function                                                 |                     |

| 01                             | AD5547-EP                                 | Dual current output, parallel input, 16 with 4-quadrant resistor | bit multiplying DAC |

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95      | Package style                     |

|----------------|----------------|-------------------|-----------------------------------|

| х              | 38             | JEDEC MO-153-BD-1 | Thin Shrink Small Outline Package |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator          | <u>Material</u>                                                                              |

|----------------------------|----------------------------------------------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>Z | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Other |

|                            |                                                                                              |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | 16236          | <b>V62/12651</b> |

|                       |      | REV            | PAGE 2           |

### 1.3 Absolute maximum ratings. 1/

| $V_{DD}$ to GND<br>$R_{FB}$ , $R_{OFS}$ , R1, $R_{COM}$ and VREF to GND<br>Logic inputs to GND<br>$V(I_{OUT})$ to GND<br>Input current to any pin except supplies<br>There is a statement of the sta | -18 V to +18 V<br>-0.3 V to +8 V<br>-0.3 V to V <sub>DD</sub> + 0.3 V |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Thermal resistance $(\theta_{JA}) \underline{2}/$<br>Maximum junction temperature $(T_{JMAX})$<br>Operating temperature range:<br>Storage temperature range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -55°C to +125°C                                                       |

| Lead temperature:<br>Vapor phase, 60 sec<br>Infrared, 15 sec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |

### 2. APPLICABLE DOCUMENTS

## JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

### JEP95 – Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at http://www.jedec.org or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201.)

#### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3 and table I herein.

3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | 16236          | <b>V62/12651</b> |  |

|                       |      | REV            | PAGE 3           |  |

<sup>&</sup>lt;u>1</u>/ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

<sup>&</sup>lt;u>2</u>/ Package power dissipation =  $(T_{JMAX} - T_A)/\theta_{JA}$ .

## 3.5 Diagrams.

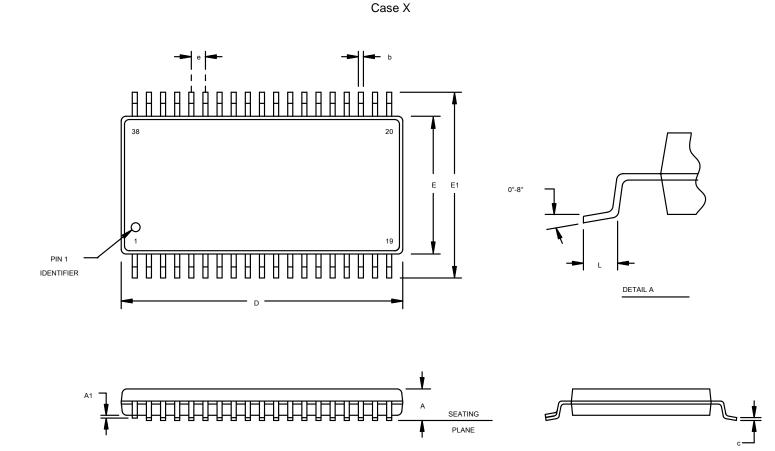

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

- 3.5.3 <u>Terminal function</u>. The terminal function shall be as shown in figure 3.

- 3.5.4 <u>Address decoder pins</u>. The truth table shall be as shown in figure 4.

- 3.5.5 <u>Control inputs</u>. The control inputs shall be as shown in figure 5.

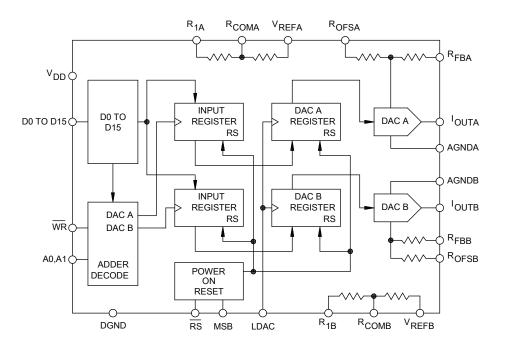

- 3.5.6 <u>Functional block diagram</u>. The functional block diagram shall be as shown in figure 6.

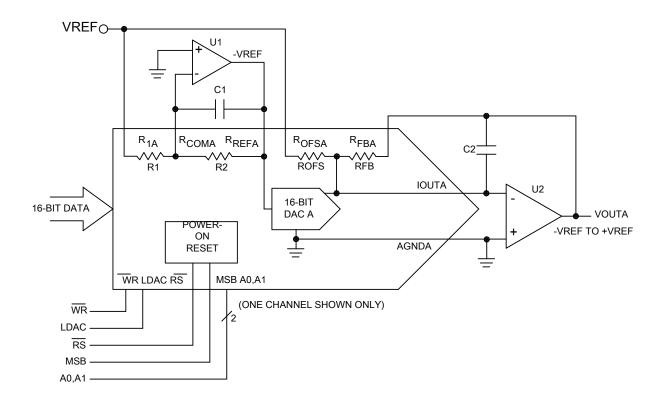

- 3.5.7 <u>16-bit 4-quadrant multiplying DAC with minimum of external components</u>. The 16-bit 4-quadrant multiplying DAC with minimum of external components shall be as shown in figure 7.

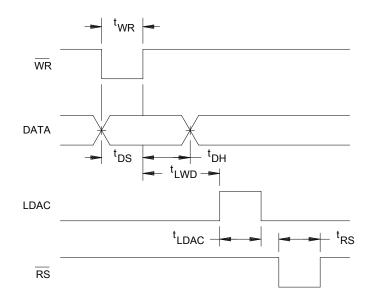

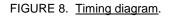

- 3.5.8 <u>Timing diagram</u>. The timing diagram shall be as shown in figure 8.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12651</b> |  |  |

|-----------------------|------|----------------|--------------------------|--|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |  |

|                       |      | REV            | PAGE 4                   |  |  |

# TABLE I. Electrical performance characteristics. 1/

| Test                                          | Symbol                             |                                                       |         | Limits |      |        |

|-----------------------------------------------|------------------------------------|-------------------------------------------------------|---------|--------|------|--------|

|                                               |                                    | <u>2</u> /                                            | Min Typ |        | Max  |        |

| Static performance <u>3</u> /                 |                                    |                                                       |         |        |      |        |

| Resolution                                    | N                                  | 1 LSB = $V_{REF}/2^{16}$ = 153 µV at $V_{REF}$ = 10 V |         | 16     |      | Bits   |

| Relative Accuracy                             | INL                                |                                                       |         |        | ±2   | LSB    |

| Differential nonlinearity                     | DNL                                | Monotonic                                             |         |        | ±1   | LSB    |

| Output leakage current                        | lout                               | Data = zero scale, $T_A = 25^{\circ}C$                |         |        | 10   | nA     |

| ouput leakage current                         | 1001                               | Data = zero scale, $T_A = T_A$ maximum                |         |        | 20   |        |

| Full scale Gain error                         | G <sub>FSE</sub>                   | Data = full scale                                     |         | ±1     | ±5   | mV     |

| Bipolar mode Gain error                       | G <sub>E</sub>                     | Data = full scale                                     |         | ±1     | ±5   |        |

| Bipolar mode Zero scale error                 | G <sub>ZSE</sub>                   | Data = full scale                                     |         | ±1     | ±4   |        |

| Full scale temperature coefficient <u>4</u> / | TCV <sub>FS</sub>                  |                                                       |         | 1      |      | ppm/°( |

| Reference input                               |                                    |                                                       |         |        |      |        |

| V <sub>REF</sub> range                        | V <sub>REF</sub>                   |                                                       | -18     |        | +18  | V      |

| REF input resistance                          | REF                                |                                                       | 4       | 5      | 6    | kΩ     |

| R1 and R2 resistance                          | R1 and R2                          |                                                       | 4       | 5      | 6    |        |

| R1 to R2 mismatch                             | Δ(R1 to R2)                        |                                                       |         | ±0.5   | ±1.5 | Ω      |

| Feedback and offset resistance                | R <sub>FB</sub> , R <sub>OFS</sub> |                                                       | 8       | 10     | 12   | kΩ     |

| Input capacitance <u>4</u> /                  | C <sub>REF</sub>                   |                                                       |         | 5      |      | pF     |

| Analog output                                 |                                    |                                                       |         |        |      |        |

| Output current                                | lout                               | Data = full scale                                     |         | 2      |      | mA     |

| Output capacitance <u>4</u> /                 | C <sub>OUT</sub>                   | Code dependent                                        |         | 200    |      | pF     |

| Logic input and output                        |                                    |                                                       |         |        |      |        |

| Logic input low voltage                       | VIL                                | $V_{DD} = 5 V$                                        |         |        | 0.8  | V      |

|                                               | VIL                                | $V_{DD} = 3 V$                                        |         |        | 0.4  |        |

| Logic input high voltage                      | V <sub>IH</sub>                    | $V_{DD} = 5 V$                                        | 2.4     |        |      |        |

|                                               | ۷IH                                | $V_{DD} = 3 V$                                        | 2.1     |        |      |        |

| Input leakage current                         | IιL                                |                                                       |         |        | 10   | μA     |

| Input capacitance <u>4</u> /                  | C <sub>IL</sub>                    |                                                       |         |        | 10   | pF     |

| Interface timing 4/ 5/ See FIGUR              | RE 8                               |                                                       |         |        |      |        |

| Data to $\overline{WR}$ setup time            | t <sub>DS</sub>                    | $V_{DD} = 5 V$                                        | 20      |        |      | ns     |

|                                               | 105                                | $V_{DD} = 3 V$                                        | 35      |        |      |        |

| Data to $\overline{WR}$ hold time             | t <sub>DS</sub>                    | $V_{DD} = 5 V$                                        | 0       |        |      |        |

|                                               | <b>U</b> S                         | $V_{DD} = 3 V$                                        | 0       |        |      |        |

| WR pulse width                                | $t_{\overline{WR}}$                | $V_{DD} = 5 V$                                        | 20      |        |      |        |

|                                               | ۳WR                                | $V_{DD} = 3 V$                                        | 35      |        |      |        |

| LDAC pulse width                              | t <sub>LDAC</sub>                  | $V_{DD} = 5 V$                                        | 20      |        |      |        |

|                                               | LDAC                               | V <sub>DD</sub> = 3 V                                 | 35      |        |      |        |

| RS pulse width                                | t <sub>RS</sub>                    | $V_{DD} = 5 V$                                        | 20      |        |      |        |

|                                               | 483                                | $V_{DD} = 3 V$                                        | 35      |        |      |        |

| WR to LDAC delay time                         | t <sub>LWD</sub>                   | $V_{DD} = 5 V$                                        | 0       |        |      |        |

|                                               | LVVD                               | $V_{DD} = 3 V$                                        | 0       |        |      |        |

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |  |

|-----------------------|------|----------------|-----------|--|

| COLUMBUS, OHIO        | A    | 16236          | V62/12651 |  |

|                       |      | REV            | PAGE 5    |  |

| TABLE I. | Electrical performance character | eristics - Continued. 1/ |

|----------|----------------------------------|--------------------------|

|----------|----------------------------------|--------------------------|

| Test                            | Symbol                             | ymbol Test conditions                              |     | Limits |       | Unit   |

|---------------------------------|------------------------------------|----------------------------------------------------|-----|--------|-------|--------|

|                                 |                                    | <u>2</u> /                                         | Min | Тур    | Max   |        |

| Supply characteristics          |                                    |                                                    |     |        |       |        |

| Power supply range              | V <sub>DD RANGE</sub>              |                                                    | 2.7 |        | 5.5   | V      |

| Power supply current            | I <sub>DD</sub>                    | Logic inputs = 0 V                                 |     |        | 10    | μA     |

| Power dissipation               | P <sub>DISS</sub>                  | Logic inputs = 0 V                                 |     |        | 0.055 | mW     |

| Power supply sensitivity        | Pss                                | $\Delta V_{DD} = \pm 5\%$                          |     |        | 0.003 | %/%    |

| AC characteristics 6/           |                                    |                                                    |     |        |       |        |

| Output voltage settling time    | ts                                 | 7/                                                 |     | 0.5    |       | μs     |

| Reference multiplying bandwidth | BW                                 | V <sub>REF</sub> = 100 mV rms, data = full scale   |     | 6.8    |       | MHz    |

| Data glitch impulse             | Q                                  | $V_{REF} = 0 V$ , midscale -1 to midscale          |     | -3.5   |       | nV-s   |

| Multiplying feedthrough error   | V <sub>OUT</sub> /V <sub>REF</sub> | $V_{REF} = 100 \text{ mV rms}, f = 10 \text{ kHz}$ |     | -78    |       | dB     |

| Digital feedthrough             | Q <sub>D</sub>                     | $\overline{WR}$ = 1, LDAC toggles at 1 MHz         |     | 7      |       | nV-s   |

| Total harmonic distortion       | THD                                | $V_{REF} = 5 V p-p$ , data = full scale, f = 1 kHz |     | -104   |       | dB     |

| Output Noise density            | e <sub>N</sub>                     | f = 1 kHz, BW = 1 Hz                               |     | 12     |       | nV/√Hz |

| Analog crosstalk                | C <sub>AT</sub>                    | 8/                                                 |     | -95    |       | dB     |

Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the 1/ specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

$V_{DD} = 2.7 \text{ V}$  to 5.5 V,  $I_{OUT} = \text{virtual GND}$ , GND = 0 V,  $V_{REF} = -10 \text{ V}$  to +10 V,  $-55^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ , unless otherwise noted. <u>2</u>/

3/ All static performance tests (except I<sub>OUT</sub>) are performed in a closed loop system using an external precision OP97 I-to V converter amplifier. The device R<sub>FB</sub> terminal is tied to the amplifier output. The +IN pin of the OP97 is grounded, and the I<sub>OUT</sub> of the DAC is tied to the OP97's -IN pin. Typical values represent average readings measured at 25°C.

Guaranteed by design, not subject to production test.

<u>4</u>/ <u>5</u>/ <u>6</u>/ All input control signals are specified with  $t_r = t_f = 2.5$  ns (10% to 90% of 3 V) and are timed from a voltage level of 1.5 V.

All ac characteristic test are performed in a closed loop system using an AD8038 I-to-V converter amplifier except for THD where the AD8065 was used.

<u>7</u>/ To ±0.1% of full scale, data cycles from zero scale to full scale to zero scale.

8/ Signal input at channel A and measures the output at channel B, f = 1 kHz.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12651</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 6                   |

| Dimensions |             |      |        |          |        |

|------------|-------------|------|--------|----------|--------|

| Symbol     | Millimeters |      | Symbol | Milli    | meters |

|            | Min         | Max  |        | Min      | Max    |

| А          |             | 1.20 | E      | 4.30     | 4.50   |

| A1         | 0.05        | 0.15 | E1     | 6.40 BSC |        |

| b          | 0.17        | 0.27 | е      | 0.50 BSC |        |

| с          | 0.09        | 0.20 | L      | 0.45     | 0.70   |

| D          | 9.60        | 9.80 |        |          |        |

# NOTES:

- All linear dimensions are in millimeters.

Falls within JEDEC MO-15-AB3.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/12651 |

|                       |      | REV            | PAGE 7    |

| Terminal | Terminal          | Terminal | Terminal               |

|----------|-------------------|----------|------------------------|

| number   | symbol            | number   | symbol                 |

| 1        | D1                | 38       | D2                     |

| 2        | D0                | 37       | D3                     |

| 3        | R <sub>OFSA</sub> | 36       | D4                     |

| 4        | $R_{FBA}$         | 35       | D5                     |

| 5        | R <sub>1A</sub>   | 34       | D6                     |

| 6        | R <sub>COMA</sub> | 33       | D7                     |

| 7        | $V_{REFA}$        | 32       | D8                     |

| 8        | I <sub>OUTA</sub> | 31       | D9                     |

| 9        | AGNDA             | 30       | D10                    |

| 10       | DGND              | 29       | VDD                    |

| 11       | AGNDA             | 28       | D11                    |

| 12       | I <sub>OUTB</sub> | 27       | D12                    |

| 13       | $V_{REFB}$        | 26       | D13                    |

| 14       | R <sub>COMB</sub> | 25       | D14                    |

| 15       | $R_{1B}$          | 24       | D15                    |

| 16       | $R_{FBB}$         | 23       | $\overline{\text{RS}}$ |

| 17       | R <sub>OFSB</sub> | 22       | MSB                    |

| 18       | WR                | 21       | LDAC                   |

| 19       | A0                | 20       | A1                     |

FIGURE 2. Terminal connections.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12651 |

|                       |      | REV            | PAGE 8    |

| Terminal                   |                   | Description                                                                                                                                                                                                                                                                            |

|----------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number                     | Mnemonic          |                                                                                                                                                                                                                                                                                        |

| 1, 2.24 to<br>28, 30 to 38 | D0 to<br>D15      | Digital input data bits D0 to D15. Signal level must be $\leq V_{DD}$ +0.3 V                                                                                                                                                                                                           |

| 3                          | R <sub>OFSA</sub> | Bipolar offset resistor A. Accepts up to $\pm 18$ V. In 2-qudarant mode, R <sub>OFSA</sub> ties to R <sub>FBA</sub> . In 4-qudarant mode, R <sub>OFSA</sub> ties to R <sub>1A</sub> and the external reference.                                                                        |

| 4                          | R <sub>FBA</sub>  | Internal matching feedback resistor A. Connects to the external op amp for I-to-V conversion.                                                                                                                                                                                          |

| 5                          | R <sub>1A</sub>   | 4-Quadrant resistor. In 2-quadrant mode, $R_{1A}$ shorts to the $V_{REFA}$ pin. In 4-quadrant mode, $R_{1A}$ ties to $R_{OFSA}$ . Do not connect when operating in unipolar mode.                                                                                                      |

| 6                          | R <sub>COMA</sub> | Center tap point of the two 4-quadrant resistor, $R_{1A}$ and $R_{2A}$ . In 4-quadrant mode, $R_{COMA}$ ties to the inverting node of the reference amplifier. In 2-quadrant mode, $R_{COMA}$ shorts to the associated $V_{REFA}$ pin. Do not connect when operating in unipolar mode. |

| 7                          | Vrefa             | DAC A reference input in 2 Quadrant mode, R2 terminal in 4-quadrant mode. In 2-quadrant mode, V <sub>REFA</sub> is the reference input with constant input resistance vs code. In 4-quadrant mode, V <sub>REFA</sub> is driven by the external reference amplifier.                    |

| 8                          | I <sub>OUTA</sub> | DAC A current output. Connects to the inverting terminal of external precision I-to-V op amp for voltage output.                                                                                                                                                                       |

| 9                          | AGNDA             | DAC A analog ground.                                                                                                                                                                                                                                                                   |

| 10                         | DGND              | Digital ground.                                                                                                                                                                                                                                                                        |

| 11                         | AGNDA             | DAC B analog ground.                                                                                                                                                                                                                                                                   |

| 12                         | I <sub>OUTB</sub> | DAC B current output. Connects to the inverting terminal of external precision I-to-V op amp for voltage output                                                                                                                                                                        |

| 13                         | $V_{REFB}$        | DAC B reference input pin. Establishes DAC full scale voltage. Constant input resistance vs code. If configured with an external op amp for 4-quadrant multiplying, $V_{REFB}$ becomes $-V_{REF}$ .                                                                                    |

| 14                         | R <sub>COMB</sub> | Center tap point of the two 4-quadrant resistor, $R_{1B}$ and $R_{2B}$ . In 4-quadrant mode, $R_{COMB}$ ties to the inverting node of the reference amplifier. In 2-quadrant mode, $R_{COMB}$ shorts to the associated $V_{REFB}$ pin. Do not connect when operating in unipolar mode. |

| 15                         | $R_{1B}$          | 4-Quadrant resistor. In 2-quadrant mode, $R_{1B}$ shorts to the $V_{REFB}$ pin. In 4-quadrant mode, $R_{1B}$ ties to $R_{OFSAB}$ . Do not connect when operating in unipolar mode.                                                                                                     |

| 16                         | R <sub>FBB</sub>  | Internal matching feedback resistor B. Connects to the external op amp for I-to-V conversion.                                                                                                                                                                                          |

| 17                         | R <sub>OFSB</sub> | Bipolar offset resistor B. Accepts up to $\pm 18$ V. In 2-qudarant mode, R <sub>OFSB</sub> ties to R <sub>FBB</sub> . In 4-qudarant mode, R <sub>OFSB</sub> ties to R <sub>1B</sub> and the external reference.                                                                        |

| 18                         | WR                | Write control digital input In, Active low. $\overline{WR}$ transfer shift register data to the DAC register on the rising edge.<br>Signal level must be $\leq V_{DD} + 0.3 V$ .                                                                                                       |

| 19                         | A0                | Address pin 0. Signal level must be $\leq V_{DD} + 0.3 V$ .                                                                                                                                                                                                                            |

| 20                         | A1                | Address pin 1. Signal level must be $\leq V_{DD} + 0.3 V$ .                                                                                                                                                                                                                            |

| 21                         | LDAC              | Digital input load DAC control. Signal level must be $\leq V_{DD} + 0.3 V$ .                                                                                                                                                                                                           |

| 22                         | MSB               | Power-On Reset State. MSB = 0 corresponds to zero scale reset; MSB = 1 corresponds to midscale reset.<br>The signal level must be $\leq V_{DD} + 0.3 \text{ V}$ .                                                                                                                      |

| 23                         | RS                | Active low resets both input and DAC registers. Reset to zero scale if MSB = 0 and reset to midscale if MSB = 1. Signal level must be $\leq V_{DD} + 0.3$ V.                                                                                                                           |

| 29                         | V <sub>DD</sub>   | Positive power supply input. The specified range of operation is 2.7 V to 5.5 V.                                                                                                                                                                                                       |

FIGURE 3. Terminal function.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12651</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | 16236          |                          |  |

|                       |      | REV            | PAGE 9                   |  |

| A1 | A0 | Output update   |

|----|----|-----------------|

| 0  | 0  | DAC A           |

| 0  | 1  | None            |

| 1  | 0  | DAC A and DAC B |

| 1  | 1  | DAC B           |

| FIGURE 4. Address decoder pins |

|--------------------------------|

|--------------------------------|

| RS | WR | LDAC | Register Operation                                                                                                                                                                                                                      |

|----|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | Х  | Х    | Reset the output to 0 with MSB = 0; reset the output to midscale with MSB = 1                                                                                                                                                           |

| 1  | 0  | 0    | Load the input register with data bits.                                                                                                                                                                                                 |

| 1  | 1  | 1    | Load the DAC register with the contents of the input register.                                                                                                                                                                          |

| 1  | 0  | 1    | The input and DAC registers are transparent.                                                                                                                                                                                            |

| 1  |    |      | When LDAC and $\overline{WR}$ are tied together and programmed as a pulse, the data bits are loaded into the input register on the falling edge of the pulse and are then loaded into the DAC register on the rising edge of the pulse. |

| 1  | 1  | 0    | No register operation                                                                                                                                                                                                                   |

## FIGURE 5. Control Inputs

| FIGURE 6. | <b>Functional</b> | block | diagram. |

|-----------|-------------------|-------|----------|

|           |                   |       |          |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12651</b> |

|                       |      | REV            | PAGE 10          |

FIGURE 7. 16-bit 4-quadrant multiplying DAC with minimum of external components.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | 16236          | <b>V62/12651</b> |

|                       |      | REV            | PAGE 11          |

### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

## 5. PREPARATION FOR DELIVERY

5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

### 6. NOTES

6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <u>http://www.landandmaritime.dla.mil/Programs/Smcr/</u>.

| Vendor item drawing<br>administrative control<br>number <u>1</u> / | Device<br>manufacturer<br>CAGE code | Vendor part number |

|--------------------------------------------------------------------|-------------------------------------|--------------------|

| V62/12651-01XB                                                     | 24355                               | AD5547SRU-EP       |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

#### CAGE code

24355

Source of supply

Analog Devices 1 Technology Way P.O. Box 9106 Norwood, MA 02062-9106

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | 16236          | <b>V62/12651</b> |

|                       |      | REV            | PAGE 12          |